Ha Neul Park

- (217)721-0562

- hnpark2@illinois.edu

- skypark.me

- Champaign, Illinois, USA

I am a Ph.D. student in Electrical and Computer Engineering at the University of Illinois Urbana-Champaign. My research interest lies in systems architecture with a special focus on memory and network subsystems.

You can find PDF version of my CV here.

Publications

Experience

Interference‑Aware LLC Orchestration in Datacenter Servers

Graduate Research Assistant

- Advised by Prof. Nam Sung Kim, FAST Lab @ UIUC

- Analyzing various LLC interference patterns with the presence of multiple I/O devices in the real system

- Reverse-engineering Intel SkyLake cache hierarchy, focused on the non-inclusiveness and the directory structure

- Implemented the DMA leakage \& QoS aware LLC management system

- Manuscript in progress to the ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS) , 2025

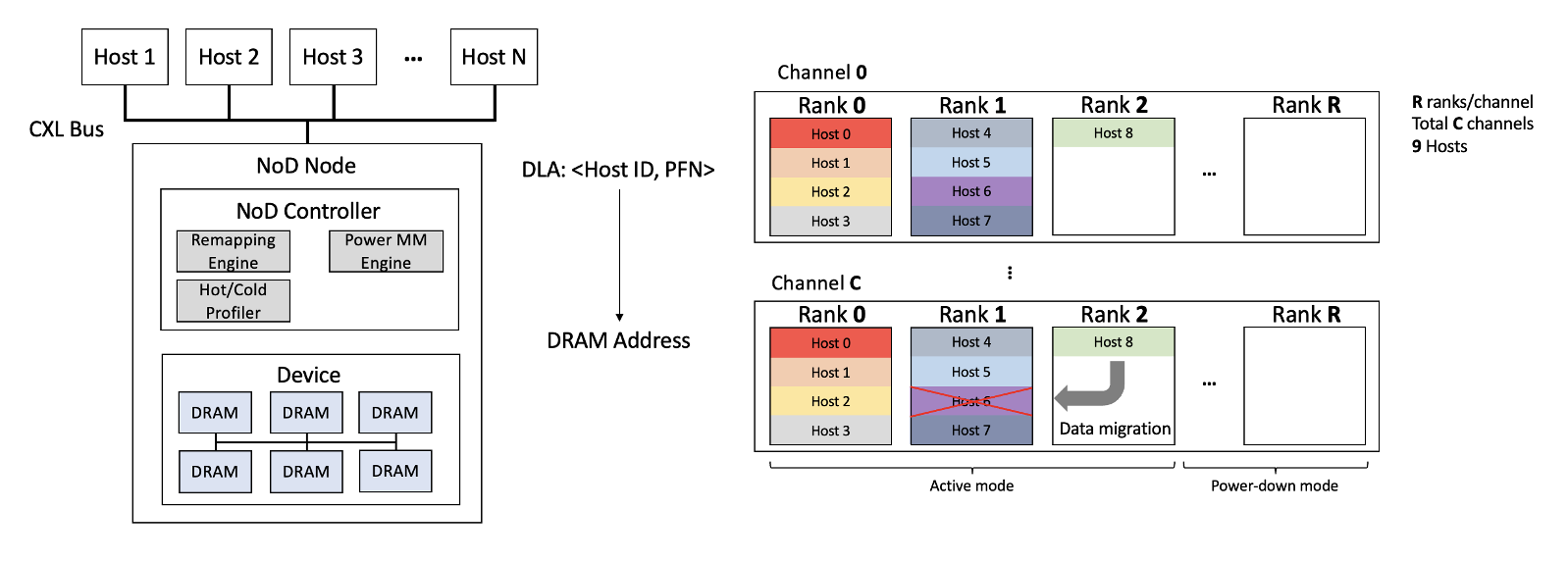

Operating System Transparent DRAM Power Management for Disaggregated Memory

Undergraduate Researcher

- Advised by Prof. Jae W. Lee, Architecture and Code Optimization Lab @ SNU

- Conducted experiment scheduling virtual machines running Cloudsuite 4.0 on an actual machine configuration that can sufficiently represent the major features of the suggested non-configurable system

- Proposed estimation methodology for performance and DRAM power metrics of suggested system, where metrics are obtained using PCM(Performance Counter Monitor)

- Fine-tuned Cloudsuite 4.0 workloads to work correctly on trace generation using binary instrumentation, INTEL PIN

- Published in ISCA 2023

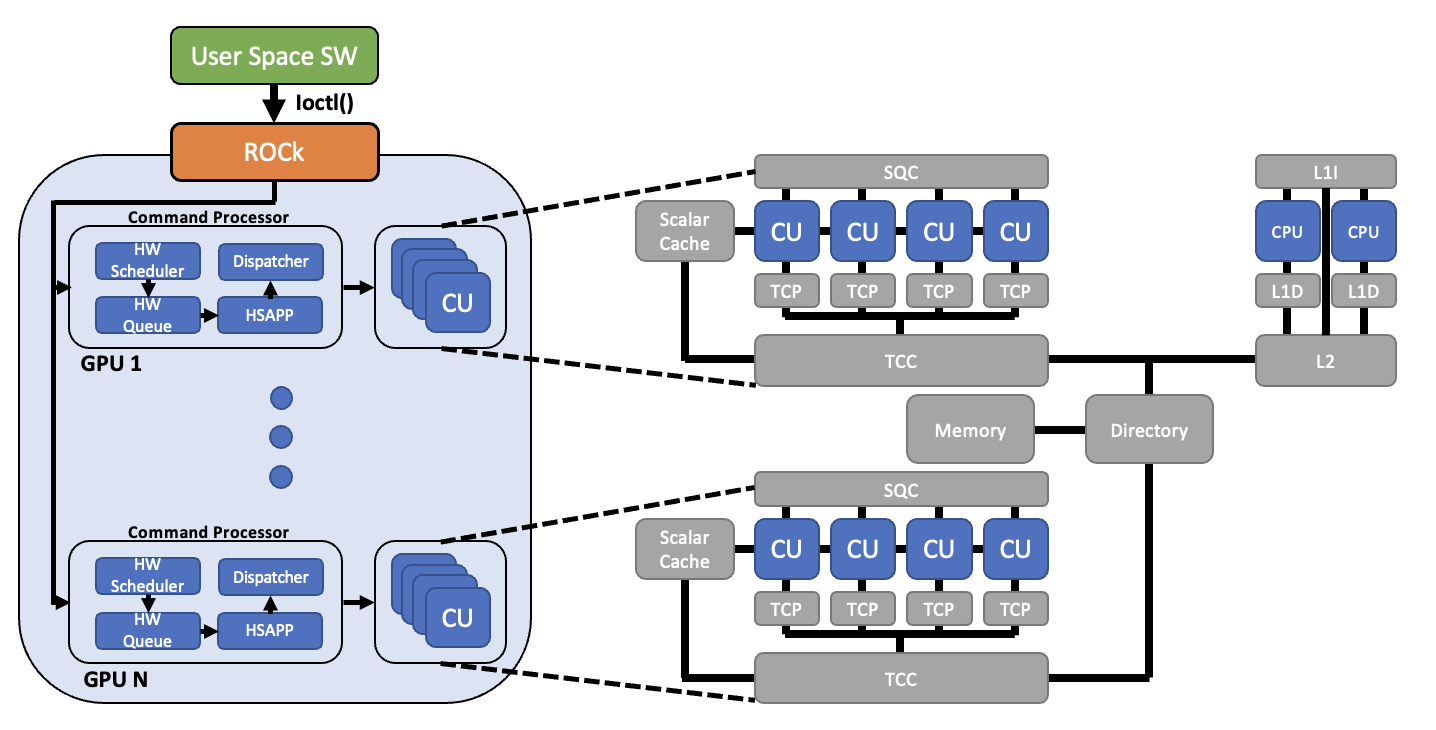

Enabling Multi-GPU Support on Gem5

Senior Project

- Advised by Prof. Jangwoo Kim, High Performance Computer System Lab @ SNU

- Extended existing gem5 GPU model by duplicating GPUs and rearranging Ruby memory interface

- Modified emulated kernel driver to distinguish GPU ID and doorbell region of each GPU from others

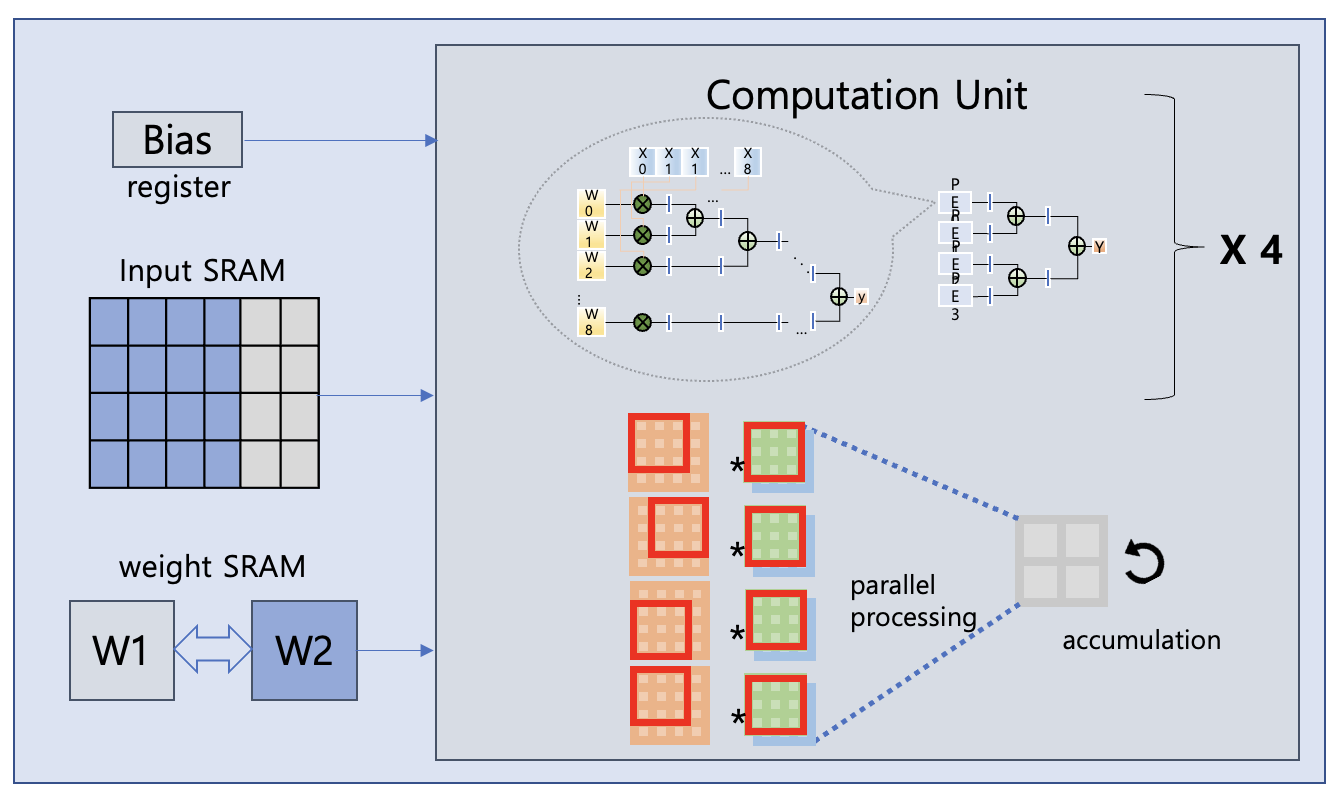

Designing AI Accelerator on FPGA

2nd place, 2022 Deep Learning hardware Design Competition

- Organized presentation for special session in IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2022

- Designed high-performance and power-efficient FPGA implementation for CNN inference

- Designed an adder-tree-based computational unit tailored to Tiny-YOLO v3 model that computes convolutions in parallel and consumes minimal cycles

- Designed the datapath to minimize the buffer usage and maximize computational parallelism, achieving maximum performance with limited on-chip memory

Honors and Awards

Artificial Intelligence Xelerator (AIX) Design Contest, 2nd prize

Nation-wide contest organized by POLARIS, a university union for semiconductor evolution

OK Bae & Jung Scholarship

OK Foundation, 9M KRW per year for undergraduate course

Presidential Science Scholarship

KOSAF, Fully funded scholarship and additional 5M KRW per year for undergraduate course

16th Korean Young Physicists' Tournament (KYPT), 3rd prize

Winter program for International Physics Olympiad (IPhO) candidates

Teaching

Calculus 1 & Calculus 2

Peer tutor, Provided 30 hours of lecture for freshman

Engineering Mathematics 1

Peer tutor, Provided 30 hours of lecture for sophomore/junior

Extracurricular

Auxiliary Police

Served as Network Maintenance Engineer at Seoul Mobile Police HeadquartersCompleted South Korea’s mandatory military service taking a leave of absence from university

Volunteer Activity

Total 338 hours, consists mostly of teaching activities